以太网驱动的流程浅析(四)-以太网驱动probe流程

作者:heaven 发布于:2020-1-7 14:25 分类:Linux内核分析

我们继续沿着上一篇的以太网思路来继续分析,目的是为了学习以太网这块从应用层到底层的整块加载和匹配流程。

如下是本人调试过程中的一点经验分享,以太网驱动架构毕竟涉及的东西太多,如下仅仅是针对加载流程和围绕这个问题产生的分析过程和驱动加载流程部分,并不涉及以太网协议层的数据流程分析。

【硬件环境】 Imx6ul

【Linux kernel版本】 Linux4.1.15

【以太网phy】 Realtek8201f

1. 以太网驱动probe流程

1.1 以太网初始化

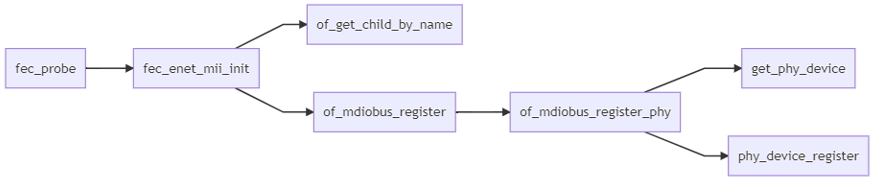

fec_main.c fec_probe

=>fec_enet_mii_init

=>of_get_child_by_name(pdev->dev.of_node, "mdio");

of_mdiobus_register(fep->mii_bus, node);

=>rc = of_mdiobus_register_phy(mdio, child, addr);

=> phy = get_phy_device(mdio, addr, is_c45);

rc = phy_device_register(phy);

搞驱动的都知道,probe是drvier的入口函数:

static int

fec_probe(struct platform_device *pdev)

{

struct fec_enet_private *fep;

struct fec_platform_data *pdata;

struct net_device *ndev;

int i, irq, ret = 0;

struct resource *r;

const struct of_device_id *of_id;

static int dev_id;

struct device_node *np = pdev->dev.of_node, *phy_node;

int num_tx_qs;

int num_rx_qs;

fec_enet_get_queue_num(pdev, &num_tx_qs, &num_rx_qs);

/* Init network device */

ndev = alloc_etherdev_mqs(sizeof(struct fec_enet_private),

num_tx_qs, num_rx_qs);

if (!ndev)

return -ENOMEM;

SET_NETDEV_DEV(ndev, &pdev->dev);

/* setup board info structure */

fep = netdev_priv(ndev);

of_id = of_match_device(fec_dt_ids, &pdev->dev);

if (of_id)

pdev->id_entry = of_id->data;

fep->quirks = pdev->id_entry->driver_data;

fep->netdev = ndev;

fep->num_rx_queues = num_rx_qs;

fep->num_tx_queues = num_tx_qs;

#if !defined(CONFIG_M5272)

/* default enable pause frame auto negotiation */

if (fep->quirks & FEC_QUIRK_HAS_GBIT)

fep->pause_flag |= FEC_PAUSE_FLAG_AUTONEG;

#endif

/* Select default pin state */

pinctrl_pm_select_default_state(&pdev->dev);

r = platform_get_resource(pdev, IORESOURCE_MEM, 0);

fep->hwp = devm_ioremap_resource(&pdev->dev, r);

if (IS_ERR(fep->hwp)) {

ret = PTR_ERR(fep->hwp);

goto failed_ioremap;

}

fep->pdev = pdev;

fep->dev_id = dev_id++;

platform_set_drvdata(pdev, ndev);

fec_enet_of_parse_stop_mode(pdev);

if (of_get_property(np, "fsl,magic-packet", NULL))

fep->wol_flag |= FEC_WOL_HAS_MAGIC_PACKET;

phy_node = of_parse_phandle(np, "phy-handle", 0);

if (!phy_node && of_phy_is_fixed_link(np)) {

ret = of_phy_register_fixed_link(np);

if (ret < 0) {

dev_err(&pdev->dev,

"broken fixed-link specification\n");

goto failed_phy;

}

phy_node = of_node_get(np);

}

fep->phy_node = phy_node;

ret = of_get_phy_mode(pdev->dev.of_node);

if (ret < 0) {

pdata = dev_get_platdata(&pdev->dev);

if (pdata)

fep->phy_interface = pdata->phy;

else

fep->phy_interface = PHY_INTERFACE_MODE_MII;

} else {

fep->phy_interface = ret;

}

fep->clk_ipg = devm_clk_get(&pdev->dev, "ipg");

if (IS_ERR(fep->clk_ipg)) {

ret = PTR_ERR(fep->clk_ipg);

goto failed_clk;

}

fep->clk_ahb = devm_clk_get(&pdev->dev, "ahb");

if (IS_ERR(fep->clk_ahb)) {

ret = PTR_ERR(fep->clk_ahb);

goto failed_clk;

}

fep->itr_clk_rate = clk_get_rate(fep->clk_ahb);

/* enet_out is optional, depends on board */

fep->clk_enet_out = devm_clk_get(&pdev->dev, "enet_out");

if (IS_ERR(fep->clk_enet_out))

fep->clk_enet_out = NULL;

fep->ptp_clk_on = false;

mutex_init(&fep->ptp_clk_mutex);

/* clk_ref is optional, depends on board */

fep->clk_ref = devm_clk_get(&pdev->dev, "enet_clk_ref");

if (IS_ERR(fep->clk_ref))

fep->clk_ref = NULL;

fep->bufdesc_ex = fep->quirks & FEC_QUIRK_HAS_BUFDESC_EX;

fep->clk_ptp = devm_clk_get(&pdev->dev, "ptp");

if (IS_ERR(fep->clk_ptp)) {

fep->clk_ptp = NULL;

fep->bufdesc_ex = false;

}

pm_runtime_enable(&pdev->dev);

ret = fec_enet_clk_enable(ndev, true);

if (ret)

goto failed_clk;

fep->reg_phy = devm_regulator_get(&pdev->dev, "phy");

if (!IS_ERR(fep->reg_phy)) {

ret = regulator_enable(fep->reg_phy);

if (ret) {

dev_err(&pdev->dev,

"Failed to enable phy regulator: %d\n", ret);

goto failed_regulator;

}

} else {

fep->reg_phy = NULL;

}

fec_reset_phy(pdev);

if (fep->bufdesc_ex)

fec_ptp_init(pdev);

ret = fec_enet_init(ndev);

if (ret)

goto failed_init;

for (i = 0; i < FEC_IRQ_NUM; i++) {

irq = platform_get_irq(pdev, i);

if (irq < 0) {

if (i)

break;

ret = irq;

goto failed_irq;

}

ret = devm_request_irq(&pdev->dev, irq, fec_enet_interrupt,

0, pdev->name, ndev);

if (ret)

goto failed_irq;

fep->irq[i] = irq;

}

ret = of_property_read_u32(np, "fsl,wakeup_irq", &irq);

if (!ret && irq < FEC_IRQ_NUM)

fep->wake_irq = fep->irq[irq];

else

fep->wake_irq = fep->irq[0];

init_completion(&fep->mdio_done);

ret = fec_enet_mii_init(pdev);

if (ret)

goto failed_mii_init;

/* Carrier starts down, phylib will bring it up */

netif_carrier_off(ndev);

fec_enet_clk_enable(ndev, false);

pinctrl_pm_select_sleep_state(&pdev->dev);

ret = register_netdev(ndev);

if (ret)

goto failed_register;

device_init_wakeup(&ndev->dev, fep->wol_flag &

FEC_WOL_HAS_MAGIC_PACKET);

if (fep->bufdesc_ex && fep->ptp_clock)

netdev_info(ndev, "registered PHC device %d\n", fep->dev_id);

fep->rx_copybreak = COPYBREAK_DEFAULT;

INIT_WORK(&fep->tx_timeout_work, fec_enet_timeout_work);

return 0;

failed_register:

fec_enet_mii_remove(fep);

failed_mii_init:

failed_irq:

failed_init:

if (fep->reg_phy)

regulator_disable(fep->reg_phy);

failed_regulator:

fec_enet_clk_enable(ndev, false);

failed_clk:

failed_phy:

of_node_put(phy_node);

failed_ioremap:

free_netdev(ndev);

return ret;

}

这个 probe中主要做了哪些事情呢?以下我只写主要的一些,不是全部的。

struct net_device *ndev;这里对net_device进行初始化,分配内存

/* Init network device */ ndev = alloc_etherdev_mqs(sizeof(struct fec_enet_private), num_tx_qs, num_rx_qs); if (!ndev) return -ENOMEM;

接下来做如下动作,注释都很明显,我就不解释了,

struct fec_enet_private *fep;

struct fec_enet_private *fep;

/* setup board info structure */ fep = netdev_priv(ndev);/** * netdev_priv - access network device private data * @dev: network device * * Get network device private data */ static inline void *netdev_priv(const struct net_device *dev) { return (char *)dev + ALIGN(sizeof(struct net_device), NETDEV_ALIGN); }

获取时钟:

fep->clk_ipg = devm_clk_get(&pdev->dev, "ipg");

if (IS_ERR(fep->clk_ipg)) {

ret = PTR_ERR(fep->clk_ipg);

goto failed_clk;

}

fep->clk_ahb = devm_clk_get(&pdev->dev, "ahb");

if (IS_ERR(fep->clk_ahb)) {

ret = PTR_ERR(fep->clk_ahb);

goto failed_clk;

}

fep->itr_clk_rate = clk_get_rate(fep->clk_ahb);

/* enet_out is optional, depends on board */

fep->clk_enet_out = devm_clk_get(&pdev->dev, "enet_out");

if (IS_ERR(fep->clk_enet_out))

fep->clk_enet_out = NULL;

fep->ptp_clk_on = false;

mutex_init(&fep->ptp_clk_mutex);

/* clk_ref is optional, depends on board */

fep->clk_ref = devm_clk_get(&pdev->dev, "enet_clk_ref");

if (IS_ERR(fep->clk_ref))

fep->clk_ref = NULL;

fep->bufdesc_ex = fep->quirks & FEC_QUIRK_HAS_BUFDESC_EX;

fep->clk_ptp = devm_clk_get(&pdev->dev, "ptp");

if (IS_ERR(fep->clk_ptp)) {

fep->clk_ptp = NULL;

fep->bufdesc_ex = false;

}

pm_runtime_enable(&pdev->dev);

ret = fec_enet_clk_enable(ndev, true);

if (ret)

goto failed_clk;

使能clk,fec_enet_clk_enable(ndev, true);

复位phy,硬件复位,具体取决于不同phy的datasheet的reset时序,fec_reset_phy(pdev);

一些初始化动作,fec_enet_init(ndev);由于代码注释写的很好,上代码:

/*

* XXX: We need to clean up on failure exits here.

*

*/

static int fec_enet_init(struct net_device *ndev)

{

struct fec_enet_private *fep = netdev_priv(ndev);

struct fec_enet_priv_tx_q *txq;

struct fec_enet_priv_rx_q *rxq;

struct bufdesc *cbd_base;

dma_addr_t bd_dma;

int bd_size;

unsigned int i;

#if defined(CONFIG_ARM)

fep->rx_align = 0xf;

fep->tx_align = 0xf;

#else

fep->rx_align = 0x3;

fep->tx_align = 0x3;

#endif

fec_enet_alloc_queue(ndev);

if (fep->bufdesc_ex)

fep->bufdesc_size = sizeof(struct bufdesc_ex);

else

fep->bufdesc_size = sizeof(struct bufdesc);

bd_size = (fep->total_tx_ring_size + fep->total_rx_ring_size) *

fep->bufdesc_size;

/* Allocate memory for buffer descriptors. */

cbd_base = dma_alloc_coherent(NULL, bd_size, &bd_dma,

GFP_KERNEL);

if (!cbd_base) {

return -ENOMEM;

}

memset(cbd_base, 0, bd_size);

/* Get the Ethernet address */

fec_get_mac(ndev);

/* make sure MAC we just acquired is programmed into the hw */

fec_set_mac_address(ndev, NULL);

/* Set receive and transmit descriptor base. */

for (i = 0; i < fep->num_rx_queues; i++) {

rxq = fep->rx_queue[i];

rxq->index = i;

rxq->rx_bd_base = (struct bufdesc *)cbd_base;

rxq->bd_dma = bd_dma;

if (fep->bufdesc_ex) {

bd_dma += sizeof(struct bufdesc_ex) * rxq->rx_ring_size;

cbd_base = (struct bufdesc *)

(((struct bufdesc_ex *)cbd_base) + rxq->rx_ring_size);

} else {

bd_dma += sizeof(struct bufdesc) * rxq->rx_ring_size;

cbd_base += rxq->rx_ring_size;

}

}

for (i = 0; i < fep->num_tx_queues; i++) {

txq = fep->tx_queue[i];

txq->index = i;

txq->tx_bd_base = (struct bufdesc *)cbd_base;

txq->bd_dma = bd_dma;

if (fep->bufdesc_ex) {

bd_dma += sizeof(struct bufdesc_ex) * txq->tx_ring_size;

cbd_base = (struct bufdesc *)

(((struct bufdesc_ex *)cbd_base) + txq->tx_ring_size);

} else {

bd_dma += sizeof(struct bufdesc) * txq->tx_ring_size;

cbd_base += txq->tx_ring_size;

}

}

/* The FEC Ethernet specific entries in the device structure */

ndev->watchdog_timeo = TX_TIMEOUT;

ndev->netdev_ops = &fec_netdev_ops;

ndev->ethtool_ops = &fec_enet_ethtool_ops;

writel(FEC_RX_DISABLED_IMASK, fep->hwp + FEC_IMASK);

netif_napi_add(ndev, &fep->napi, fec_enet_rx_napi, NAPI_POLL_WEIGHT);

if (fep->quirks & FEC_QUIRK_HAS_VLAN)

/* enable hw VLAN support */

ndev->features |= NETIF_F_HW_VLAN_CTAG_RX;

if (fep->quirks & FEC_QUIRK_HAS_CSUM) {

ndev->gso_max_segs = FEC_MAX_TSO_SEGS;

/* enable hw accelerator */

ndev->features |= (NETIF_F_IP_CSUM | NETIF_F_IPV6_CSUM

| NETIF_F_RXCSUM | NETIF_F_SG | NETIF_F_TSO);

fep->csum_flags |= FLAG_RX_CSUM_ENABLED;

}

if (fep->quirks & FEC_QUIRK_HAS_AVB) {

fep->tx_align = 0;

fep->rx_align = 0x3f;

}

ndev->hw_features = ndev->features;

fec_restart(ndev);

return 0;

}

1.2 获取以太网mac地址

/* Get the Ethernet address */ fec_get_mac(ndev); /* make sure MAC we just acquired is programmed into the hw */ fec_set_mac_address(ndev, NULL);

这里获取mac 地址的流程我要说一下,之前有讲过流程,我这里再提一下:

1) 模块化参数设置,如果没有跳到步骤2

static void fec_get_mac(struct net_device *ndev)

{

struct fec_enet_private *fep = netdev_priv(ndev);

struct fec_platform_data *pdata = dev_get_platdata(&fep->pdev->dev);

unsigned char *iap, tmpaddr[ETH_ALEN];

/*

* try to get mac address in following order:

*

* 1) module parameter via kernel command line in form

* fec.macaddr=0x00,0x04,0x9f,0x01,0x30,0xe0

*/

iap = macaddr;

2) device tree中设置,如果没有跳到步骤3;

/*

* 2) from device tree data

*/

if (!is_valid_ether_addr(iap)) {

struct device_node *np = fep->pdev->dev.of_node;

if (np) {

const char *mac = of_get_mac_address(np);

if (mac)

iap = (unsigned char *) mac;

}

}

3) from flash / fuse / via platform data,如果没有跳到步骤4;

/*

* 3) from flash or fuse (via platform data)

*/

if (!is_valid_ether_addr(iap)) {

#ifdef CONFIG_M5272

if (FEC_FLASHMAC)

iap = (unsigned char *)FEC_FLASHMAC;

#else

if (pdata)

iap = (unsigned char *)&pdata->mac;

#endif

}

4) FEC mac registers set by bootloader===》即靠usb方式下载mac address ,如果没有跳到步骤5;

/*

* 4) FEC mac registers set by bootloader

*/

if (!is_valid_ether_addr(iap)) {

*((__be32 *) &tmpaddr[0]) =

cpu_to_be32(readl(fep->hwp + FEC_ADDR_LOW));

*((__be16 *) &tmpaddr[4]) =

cpu_to_be16(readl(fep->hwp + FEC_ADDR_HIGH) >> 16);

iap = &tmpaddr[0];

}

5)靠kernel算一个随机数mac address出来,然后写入mac

/*

* 5) random mac address

*/

if (!is_valid_ether_addr(iap)) {

/* Report it and use a random ethernet address instead */

netdev_err(ndev, "Invalid MAC address: %pM\n", iap);

eth_hw_addr_random(ndev);

netdev_info(ndev, "Using random MAC address: %pM\n",

ndev->dev_addr);

return;

}

memcpy(ndev->dev_addr, iap, ETH_ALEN);

/* Adjust MAC if using macaddr */

if (iap == macaddr)

ndev->dev_addr[ETH_ALEN-1] = macaddr[ETH_ALEN-1] + fep->dev_id;

所以最后一种方式就是kernel会自己算一个mac地址出来,我这里有个前提是这个是freescale(现在被nxp收购了)的控制器代码这样写的,我不确定其他厂商的控制器是否也是这样的流程,技术讲究严谨,所以这里不能一概而论。当然这个mac 地址也是可以用户自己在dts中进行自行配置的。

/** * eth_hw_addr_random - Generate software assigned random Ethernet and * set device flag * @dev: pointer to net_device structure * * Generate a random Ethernet address (MAC) to be used by a net device * and set addr_assign_type so the state can be read by sysfs and be * used by userspace. */ static inline void eth_hw_addr_random(struct net_device *dev) { dev->addr_assign_type = NET_ADDR_RANDOM; eth_random_addr(dev->dev_addr); }/** * eth_random_addr - Generate software assigned random Ethernet address * @addr: Pointer to a six-byte array containing the Ethernet address * * Generate a random Ethernet address (MAC) that is not multicast * and has the local assigned bit set. */ static inline void eth_random_addr(u8 *addr) { get_random_bytes(addr, ETH_ALEN); addr[0] &= 0xfe; /* clear multicast bit */ addr[0] |= 0x02; /* set local assignment bit (IEEE802) */ }

这里就是kernel随机数的接口了,会总随机池中获取一个随机数并返回。

/*

* This function is the exported kernel interface. It returns some

* number of good random numbers, suitable for key generation, seeding

* TCP sequence numbers, etc. It does not rely on the hardware random

* number generator. For random bytes direct from the hardware RNG

* (when available), use get_random_bytes_arch().

*/

void get_random_bytes(void *buf, int nbytes)

{

#if DEBUG_RANDOM_BOOT > 0

if (unlikely(nonblocking_pool.initialized == 0))

printk(KERN_NOTICE "random: %pF get_random_bytes called "

"with %d bits of entropy available\n",

(void *) _RET_IP_,

nonblocking_pool.entropy_total);

#endif

trace_get_random_bytes(nbytes, _RET_IP_);

extract_entropy(&nonblocking_pool, buf, nbytes, 0, 0);

}

EXPORT_SYMBOL(get_random_bytes);

大家看到那些获取mac address的步骤中有这样的函数

is_valid_ether_addr,用来检测以太网地址是否正确的

/**

* is_valid_ether_addr - Determine if the given Ethernet address is valid

* @addr: Pointer to a six-byte array containing the Ethernet address

*

* Check that the Ethernet address (MAC) is not 00:00:00:00:00:00, is not

* a multicast address, and is not FF:FF:FF:FF:FF:FF.

*

* Return true if the address is valid.

*

* Please note: addr must be aligned to u16.

*/

static inline bool is_valid_ether_addr(const u8 *addr)

{

/* FF:FF:FF:FF:FF:FF is a multicast address so we don't need to

* explicitly check for it here. */

return !is_multicast_ether_addr(addr) && !is_zero_ether_addr(addr);

}

因此我们从代码中可以看出,内核认为全0或者是全FF的以太网地址是不正确的,

获取了mac 地址后,就会通过寄存器写入mac中

/* Set a MAC change in hardware. */

static int

fec_set_mac_address(struct net_device *ndev, void *p)

{

struct fec_enet_private *fep = netdev_priv(ndev);

struct sockaddr *addr = p;

if (addr) {

if (!is_valid_ether_addr(addr->sa_data))

return -EADDRNOTAVAIL;

memcpy(ndev->dev_addr, addr->sa_data, ndev->addr_len);

}

/* Add netif status check here to avoid system hang in below case:

* ifconfig ethx down; ifconfig ethx hw ether xx:xx:xx:xx:xx:xx;

* After ethx down, fec all clocks are gated off and then register

* access causes system hang.

*/

if (!netif_running(ndev))

return 0;

writel(ndev->dev_addr[3] | (ndev->dev_addr[2] << 8) |

(ndev->dev_addr[1] << 16) | (ndev->dev_addr[0] << 24),

fep->hwp + FEC_ADDR_LOW);

writel((ndev->dev_addr[5] << 16) | (ndev->dev_addr[4] << 24),

fep->hwp + FEC_ADDR_HIGH);

return 0;

}

CONFIG_ARCH_MXC因为我们使用的是这个宏,因此:

#if defined(CONFIG_M523x) || defined(CONFIG_M527x) || defined(CONFIG_M528x) || \

defined(CONFIG_M520x) || defined(CONFIG_M532x) || \

defined(CONFIG_ARCH_MXC) || defined(CONFIG_SOC_IMX28)

/*

* Just figures, Motorola would have to change the offsets for

* registers in the same peripheral device on different models

* of the ColdFire!

*/

#define FEC_IEVENT 0x004 /* Interrupt event reg */

#define FEC_IMASK 0x008 /* Interrupt mask reg */

#define FEC_R_DES_ACTIVE_0 0x010 /* Receive descriptor reg */

#define FEC_X_DES_ACTIVE_0 0x014 /* Transmit descriptor reg */

#define FEC_ECNTRL 0x024 /* Ethernet control reg */

#define FEC_MII_DATA 0x040 /* MII manage frame reg */

#define FEC_MII_SPEED 0x044 /* MII speed control reg */

#define FEC_MIB_CTRLSTAT 0x064 /* MIB control/status reg */

#define FEC_R_CNTRL 0x084 /* Receive control reg */

#define FEC_X_CNTRL 0x0c4 /* Transmit Control reg */

#define FEC_ADDR_LOW 0x0e4 /* Low 32bits MAC address */

#define FEC_ADDR_HIGH 0x0e8 /* High 16bits MAC address */

否则:

#define FEC_ADDR_LOW 0x3c0 /* Low 32bits MAC address */ #define FEC_ADDR_HIGH 0x3c4 /* High 16bits MAC address */

设置buffer传输的基地址

/* Set receive and transmit descriptor base. */

for (i = 0; i < fep->num_rx_queues; i++) {

rxq = fep->rx_queue[i];

rxq->index = i;

rxq->rx_bd_base = (struct bufdesc *)cbd_base;

rxq->bd_dma = bd_dma;

if (fep->bufdesc_ex) {

bd_dma += sizeof(struct bufdesc_ex) * rxq->rx_ring_size;

cbd_base = (struct bufdesc *)

(((struct bufdesc_ex *)cbd_base) + rxq->rx_ring_size);

} else {

bd_dma += sizeof(struct bufdesc) * rxq->rx_ring_size;

cbd_base += rxq->rx_ring_size;

}

}

for (i = 0; i < fep->num_tx_queues; i++) {

txq = fep->tx_queue[i];

txq->index = i;

txq->tx_bd_base = (struct bufdesc *)cbd_base;

txq->bd_dma = bd_dma;

if (fep->bufdesc_ex) {

bd_dma += sizeof(struct bufdesc_ex) * txq->tx_ring_size;

cbd_base = (struct bufdesc *)

(((struct bufdesc_ex *)cbd_base) + txq->tx_ring_size);

} else {

bd_dma += sizeof(struct bufdesc) * txq->tx_ring_size;

cbd_base += txq->tx_ring_size;

}

}

提供一些以太网控制器的操作接口,应用层调用socket通信最终的实现接口方式,并且提供开源工具ethtool工具的底层操作接口支持

/* The FEC Ethernet specific entries in the device structure */ ndev->watchdog_timeo = TX_TIMEOUT; ndev->netdev_ops = &fec_netdev_ops; ndev->ethtool_ops = &fec_enet_ethtool_ops;

static const struct net_device_ops fec_netdev_ops = {

.ndo_open = fec_enet_open,

.ndo_stop = fec_enet_close,

.ndo_start_xmit = fec_enet_start_xmit,

.ndo_select_queue = fec_enet_select_queue,

.ndo_set_rx_mode = set_multicast_list,

.ndo_change_mtu = eth_change_mtu,

.ndo_validate_addr = eth_validate_addr,

.ndo_tx_timeout = fec_timeout,

.ndo_set_mac_address = fec_set_mac_address,

.ndo_do_ioctl = fec_enet_ioctl,

#ifdef CONFIG_NET_POLL_CONTROLLER

.ndo_poll_controller = fec_poll_controller,

#endif

.ndo_set_features = fec_set_features,

};

static const struct ethtool_ops fec_enet_ethtool_ops = {

.get_settings = fec_enet_get_settings,

.set_settings = fec_enet_set_settings,

.get_drvinfo = fec_enet_get_drvinfo,

.get_regs_len = fec_enet_get_regs_len,

.get_regs = fec_enet_get_regs,

.nway_reset = fec_enet_nway_reset,

.get_link = ethtool_op_get_link,

.get_coalesce = fec_enet_get_coalesce,

.set_coalesce = fec_enet_set_coalesce,

#ifndef CONFIG_M5272

.get_pauseparam = fec_enet_get_pauseparam,

.set_pauseparam = fec_enet_set_pauseparam,

.get_strings = fec_enet_get_strings,

.get_ethtool_stats = fec_enet_get_ethtool_stats,

.get_sset_count = fec_enet_get_sset_count,

#endif

.get_ts_info = fec_enet_get_ts_info,

.get_tunable = fec_enet_get_tunable,

.set_tunable = fec_enet_set_tunable,

.get_wol = fec_enet_get_wol,

.set_wol = fec_enet_set_wol,

};

所以有些人用ethtool工具发现不同平台可能不一样,同样的命令有些可能返回不同,或者功能不支持,就可以猜想一下可能是因为不同厂商的控制器驱动这里的实现问题导致,部分接口可能没有实现或者有bug等等,这些就要具体问题具体分析了,有些板子可能某些接口根本都没实现,自然ethtool的一些命令就无法正常使用了。

最后进行控制器对phy的复位动作

fec_restart(ndev);

/*

* This function is called to start or restart the FEC during a link

* change, transmit timeout, or to reconfigure the FEC. The network

* packet processing for this device must be stopped before this call.

*/

static void

fec_restart(struct net_device *ndev)

{

struct fec_enet_private *fep = netdev_priv(ndev);

u32 val;

u32 temp_mac[2];

u32 rcntl = OPT_FRAME_SIZE | 0x04;

u32 ecntl = FEC_ENET_ETHEREN; /* ETHEREN */

/* Whack a reset. We should wait for this.

* For i.MX6SX SOC, enet use AXI bus, we use disable MAC

* instead of reset MAC itself.

*/

if (fep->quirks & FEC_QUIRK_HAS_AVB) {

writel(0, fep->hwp + FEC_ECNTRL);

} else {

writel(1, fep->hwp + FEC_ECNTRL);

udelay(10);

}

/*

* enet-mac reset will reset mac address registers too,

* so need to reconfigure it.

*/

if (fep->quirks & FEC_QUIRK_ENET_MAC) {

memcpy(&temp_mac, ndev->dev_addr, ETH_ALEN);

writel(cpu_to_be32(temp_mac[0]), fep->hwp + FEC_ADDR_LOW);

writel(cpu_to_be32(temp_mac[1]), fep->hwp + FEC_ADDR_HIGH);

}

/* Clear any outstanding interrupt. */

writel(0xffffffff, fep->hwp + FEC_IEVENT);

fec_enet_bd_init(ndev);

fec_enet_enable_ring(ndev);

/* Reset tx SKB buffers. */

fec_enet_reset_skb(ndev);

/* Enable MII mode */

if (fep->full_duplex == DUPLEX_FULL) {

/* FD enable */

writel(0x04, fep->hwp + FEC_X_CNTRL);

} else {

/* No Rcv on Xmit */

rcntl |= 0x02;

writel(0x0, fep->hwp + FEC_X_CNTRL);

}

/* Set MII speed */

writel(fep->phy_speed, fep->hwp + FEC_MII_SPEED);

#if !defined(CONFIG_M5272)

if (fep->quirks & FEC_QUIRK_HAS_RACC) {

/* set RX checksum */

val = readl(fep->hwp + FEC_RACC);

if (fep->csum_flags & FLAG_RX_CSUM_ENABLED)

val |= FEC_RACC_OPTIONS;

else

val &= ~FEC_RACC_OPTIONS;

writel(val, fep->hwp + FEC_RACC);

}

writel(PKT_MAXBUF_SIZE, fep->hwp + FEC_FTRL);

#endif

/*

* The phy interface and speed need to get configured

* differently on enet-mac.

*/

if (fep->quirks & FEC_QUIRK_ENET_MAC) {

/* Enable flow control and length check */

rcntl |= 0x40000000 | 0x00000020;

/* RGMII, RMII or MII */

if (fep->phy_interface == PHY_INTERFACE_MODE_RGMII ||

fep->phy_interface == PHY_INTERFACE_MODE_RGMII_ID ||

fep->phy_interface == PHY_INTERFACE_MODE_RGMII_RXID ||

fep->phy_interface == PHY_INTERFACE_MODE_RGMII_TXID)

rcntl |= (1 << 6);

else if (fep->phy_interface == PHY_INTERFACE_MODE_RMII)

rcntl |= (1 << 8);

else

rcntl &= ~(1 << 8);

/* 1G, 100M or 10M */

if (fep->phy_dev) {

if (fep->phy_dev->speed == SPEED_1000)

ecntl |= (1 << 5);

else if (fep->phy_dev->speed == SPEED_100)

rcntl &= ~(1 << 9);

else

rcntl |= (1 << 9);

}

} else {

#ifdef FEC_MIIGSK_ENR

if (fep->quirks & FEC_QUIRK_USE_GASKET) {

u32 cfgr;

/* disable the gasket and wait */

writel(0, fep->hwp + FEC_MIIGSK_ENR);

while (readl(fep->hwp + FEC_MIIGSK_ENR) & 4)

udelay(1);

/*

* configure the gasket:

* RMII, 50 MHz, no loopback, no echo

* MII, 25 MHz, no loopback, no echo

*/

cfgr = (fep->phy_interface == PHY_INTERFACE_MODE_RMII)

? BM_MIIGSK_CFGR_RMII : BM_MIIGSK_CFGR_MII;

if (fep->phy_dev && fep->phy_dev->speed == SPEED_10)

cfgr |= BM_MIIGSK_CFGR_FRCONT_10M;

writel(cfgr, fep->hwp + FEC_MIIGSK_CFGR);

/* re-enable the gasket */

writel(2, fep->hwp + FEC_MIIGSK_ENR);

}

#endif

}

#if !defined(CONFIG_M5272)

/* enable pause frame*/

if ((fep->pause_flag & FEC_PAUSE_FLAG_ENABLE) ||

((fep->pause_flag & FEC_PAUSE_FLAG_AUTONEG) &&

fep->phy_dev && fep->phy_dev->pause)) {

rcntl |= FEC_ENET_FCE;

/* set FIFO threshold parameter to reduce overrun */

writel(FEC_ENET_RSEM_V, fep->hwp + FEC_R_FIFO_RSEM);

writel(FEC_ENET_RSFL_V, fep->hwp + FEC_R_FIFO_RSFL);

writel(FEC_ENET_RAEM_V, fep->hwp + FEC_R_FIFO_RAEM);

writel(FEC_ENET_RAFL_V, fep->hwp + FEC_R_FIFO_RAFL);

/* OPD */

writel(FEC_ENET_OPD_V, fep->hwp + FEC_OPD);

} else {

rcntl &= ~FEC_ENET_FCE;

}

#endif /* !defined(CONFIG_M5272) */

writel(rcntl, fep->hwp + FEC_R_CNTRL);

/* Setup multicast filter. */

set_multicast_list(ndev);

#ifndef CONFIG_M5272

writel(0, fep->hwp + FEC_HASH_TABLE_HIGH);

writel(0, fep->hwp + FEC_HASH_TABLE_LOW);

#endif

if (fep->quirks & FEC_QUIRK_ENET_MAC) {

/* enable ENET endian swap */

ecntl |= (1 << 8);

/* enable ENET store and forward mode */

writel(1 << 8, fep->hwp + FEC_X_WMRK);

}

if (fep->bufdesc_ex)

ecntl |= (1 << 4);

#ifndef CONFIG_M5272

/* Enable the MIB statistic event counters */

writel(0 << 31, fep->hwp + FEC_MIB_CTRLSTAT);

#endif

/* And last, enable the transmit and receive processing */

writel(ecntl, fep->hwp + FEC_ECNTRL);

fec_enet_active_rxring(ndev);

if (fep->bufdesc_ex)

fec_ptp_start_cyclecounter(ndev);

/* Enable interrupts we wish to service */

if (fep->link)

writel(FEC_DEFAULT_IMASK, fep->hwp + FEC_IMASK);

else

writel(FEC_ENET_MII, fep->hwp + FEC_IMASK);

/* Init the interrupt coalescing */

fec_enet_itr_coal_init(ndev);

}

流程如下:

1) Whack a reset. We should wait for this. For i.MX6SX SOC, enet use AXI bus, we use disable MAC , instead of reset MAC itself.

2)enet-mac reset will reset mac address registers too, so need to reconfigure it.

3) Clear any outstanding interrupt.

4) Reset tx SKB buffers.

5) Enable MII mode

6) The phy interface and speed need to get configured,

7) configure the gasket: RMII, 50 MHz, no loopback, no echo; MII, 25 MHz, no loopback, no echo

8) Setup multicast filter.

9) And last, enable the transmit and receive processing

10) Enable interrupts we wish to service

11) Init the interrupt coalescing

fec_enet_init函数的流程到此结束

我们继续回归到fec_probe函数,然后是注册中断处理函数

for (i = 0; i < FEC_IRQ_NUM; i++) {

irq = platform_get_irq(pdev, i);

if (irq < 0) {

if (i)

break;

ret = irq;

goto failed_irq;

}

ret = devm_request_irq(&pdev->dev, irq, fec_enet_interrupt,

0, pdev->name, ndev);

if (ret)

goto failed_irq;

fep->irq[i] = irq;

}

1. 网址分享

http://stackoverflow.com/questions/5308090/set-ip-address-using-siocsifaddr-ioctl

https://lkml.org/lkml/2017/2/3/396

linux PHY驱动

http://www.latelee.org/programming-under-linux/linux-phy-driver.html

Linux PHY几个状态的跟踪

http://www.latelee.org/programming-under-linux/linux-phy-state.html

第十六章PHY -基于Linux3.10

https://blog.csdn.net/shichaog/article/details/44682931

功能

最新评论

文章分类

随机文章

文章存档

- 2025年4月(5)

- 2024年2月(1)

- 2023年5月(1)

- 2022年10月(1)

- 2022年8月(1)

- 2022年6月(1)

- 2022年5月(1)

- 2022年4月(2)

- 2022年2月(2)

- 2021年12月(1)

- 2021年11月(5)

- 2021年7月(1)

- 2021年6月(1)

- 2021年5月(3)

- 2020年3月(3)

- 2020年2月(2)

- 2020年1月(3)

- 2019年12月(3)

- 2019年5月(4)

- 2019年3月(1)

- 2019年1月(3)

- 2018年12月(2)

- 2018年11月(1)

- 2018年10月(2)

- 2018年8月(1)

- 2018年6月(1)

- 2018年5月(1)

- 2018年4月(7)

- 2018年2月(4)

- 2018年1月(5)

- 2017年12月(2)

- 2017年11月(2)

- 2017年10月(1)

- 2017年9月(5)

- 2017年8月(4)

- 2017年7月(4)

- 2017年6月(3)

- 2017年5月(3)

- 2017年4月(1)

- 2017年3月(8)

- 2017年2月(6)

- 2017年1月(5)

- 2016年12月(6)

- 2016年11月(11)

- 2016年10月(9)

- 2016年9月(6)

- 2016年8月(9)

- 2016年7月(5)

- 2016年6月(8)

- 2016年5月(8)

- 2016年4月(7)

- 2016年3月(5)

- 2016年2月(5)

- 2016年1月(6)

- 2015年12月(6)

- 2015年11月(9)

- 2015年10月(9)

- 2015年9月(4)

- 2015年8月(3)

- 2015年7月(7)

- 2015年6月(3)

- 2015年5月(6)

- 2015年4月(9)

- 2015年3月(9)

- 2015年2月(6)

- 2015年1月(6)

- 2014年12月(17)

- 2014年11月(8)

- 2014年10月(9)

- 2014年9月(7)

- 2014年8月(12)

- 2014年7月(6)

- 2014年6月(6)

- 2014年5月(9)

- 2014年4月(9)

- 2014年3月(7)

- 2014年2月(3)

- 2014年1月(4)

发表评论: